ICS 31.200

CCS L56

# T/CASME

团 体 标 准

T/CASME XXX—2025

## 芯片内建沟道退化监测单元电路 设计与测试规范

Design and test specification of built-in channel degradation monitoring

unit circuit in chip

(征求意见稿)

2025-XX-XX 发布

2025-XX-XX 实施

中国中小商业企业协会 发布

## 目 次

|                   |     |

|-------------------|-----|

| 前言 .....          | II  |

| 引言 .....          | III |

| 1 范围 .....        | 1   |

| 2 规范性引用文件 .....   | 1   |

| 3 术语和定义 .....     | 1   |

| 4 缩略语 .....       | 1   |

| 5 设计依据和设计准则 ..... | 1   |

| 6 监测原理 .....      | 2   |

| 7 设计程序 .....      | 3   |

| 8 电路设计 .....      | 4   |

| 9 测试验证 .....      | 5   |

| 参考文献 .....        | 7   |

## 前　　言

本文件按照GB/T 1.1—2020《标准化工作导则 第1部分：标准化文件的结构和起草规则》的规定起草。

请注意本文件的某些内容可能涉及专利。本文件的发布机构不承担识别专利的责任。

本文件由西安电子科技大学提出。

本文件由中国中小商业企业协会归口。

本文件起草单位：西安电子科技大学……

本文件主要起草人：李小明……

## 引　　言

随着半导体工艺特征尺寸的不断缩小，器件的沟道长度显著减小，沟道电场强度大幅提升。在强电场作用下，器件沟道中的载流子获得足够能量，形成热载流子。这些热载流子可能穿越势垒进入氧化层，诱发缺陷，进而导致器件乃至电路性能衰退。尽管工艺不断进步，厂商和研究者却不得不将更多注意力集中到热载流子注入效应上。例如，大多数工艺厂商在完成晶圆最后一道工序“钝化”后，都会进行晶圆级热载流子失效实验，利用实验数据调整生产工艺。与此同时，许多电路设计者在了解热载流子注入的危害后，也在电路设计中采取措施以削弱其效应。

然而，随着特征尺寸的持续缩小，热载流子注入效应的危害愈发显著，但对其引发的电路失效却难以实现及时掌控，这在某些应用领域中极为危险。为了评估器件和电路的热载流子失效寿命及热载流子效应的可靠性影响，最早由Berkeley开发了电路可靠性仿真软件BERT。但鉴于SoC规模庞大，采用软件进行可靠性仿真耗时巨大，且由于可靠性模型精度问题，仿真结果准确性欠佳。更为关键的是，它无法实时反映待测电路的可靠性状态，也无法对即将失效的电路发出告警。

鉴于此，本文件提出一种可嵌入SoC的热载流子注入失效监测技术及电路。当器件或电路因热载流子效应导致参数失效时，监测电路能够提前发出告警信号，提醒用户及时采取应对措施。

# 芯片内建沟道退化监测单元电路设计与测试规范

## 1 范围

本文件规定了芯片内建沟道退化监测单元电路的设计依据和设计准则、监测原理、设计程序、电路设计、测试验证。

本文件适用于芯片内建沟道退化监测单元电路的设计与测试。

## 2 规范性引用文件

下列文件中的内容通过文中的规范性引用而构成本文件必不可少的条款。其中，注日期的引用文件，仅该日期对应的版本适用于本文件；不注日期的引用文件，其最新版本（包括所有的修改单）适用于本文件。

GB/T 2036 印制电路术语

GB/T 9178 集成电路术语

## 3 术语和定义

GB/T 2036、GB/T 9178界定的以及下列术语和定义适用于本文件。

### 3.1 热载流子 hot carrier; HC

在强电场作用下，半导体中载流子的能量会大大提高，使其平均能量大大超过kT，即等效载流子温度T将超过晶格温度Ta，这时的载流子称为热载流子。

### 3.2 环形振荡器 ring oscillator

由三个非门或更多奇数个非门输出端和输入端首尾相接，构成环状的振荡信号发生电路。

## 4 缩略语

以下缩略语适用于本文件。

CMOS：互补金属氧化物半导体（Complementary Metal Oxide Semiconductor）

HCI：热载流子注入（Hot Carrier Injection）

MOS：金氧半场效晶体管（Metal-Oxide-Semiconductor）

NMOS：N沟道MOS晶体管（N-Channel-Metal-Oxide-Semiconductor）

## 5 设计依据和设计准则

### 5.1 设计依据

芯片内建沟道退化监测单元电路的设计应依据组件产品设计任务书和电路图以及设计规则进行。

### 5.2 设计准则

芯片内建沟道退化监测单元电路的设计基本准则主要考虑以下内容：

- a) 芯片内建沟道退化监测单元电路的关键部分——环形振荡器的构成与时序；

- b) 芯片内建沟道退化监测单元电路与主芯片应力耦合并确认提前预报量；

- c) 芯片内建沟道退化监测单元电路应避免或削弱工艺偏差、电压波动等因素对监测结果的影响；

- d) 芯片内建沟道退化监测单元电路的布局数量、功耗、输出格式应符合主芯片的集成要求；

- e) 芯片内建沟道退化监测单元电路的可靠性设计应满足设计任务书的要求或可靠性的相关规定；

- f) 芯片内建沟道退化监测单元电路的设计应符合可制造性的要求；

- g) 芯片内建沟道退化监测单元电路的设计在满足使用安全性和可靠性要求的前提下，应从设计方法、基材、制造工艺、表面镀层和涂覆层等方面考虑成本最低的原则，力求经济实用；

- h) 功率较大的芯片内建沟道退化监测单元电路应进行热设计分析，考虑环境参数、元器件特性、元器件的位置，计算出元器件结温、电路板表面温度和失效率，确保组件的可靠性；

- i) 芯片内建沟道退化监测单元电路的设计应充分考虑表面安装电路基板、组件的机械强度和应力释放，保证元器件焊点及组件能经受规定的环境条件；

- j) 芯片内建沟道退化监测单元电路的设计应充分考虑装配工艺要求和调测试要求，尽可能有利于装配、维修和测试。

6 监测原理

### 6.1 HCl 对反相器的影响

6.1.1 HCI 效应影响下的 NMOS 管，其  $\text{SiO}_2/\text{Si}$  界面及栅介质中会产生净负电荷，这些电荷会使 NMOS 管电流减小，驱动能力下降，门电路延迟退化。通过监测门电路的延迟来衡量 HCI 效应的影响，实现 HC 失效监测。

6.1.2 CMOS 传输延迟衰退随着漏电流衰退的增加而线性增加、输出下降延迟衰退也随着漏电流衰退的增加线性增加。传输延迟的衰退大于输出下降延迟，因此反相器传输延迟可作为理想的监测参数，通过对其监测就可以有效的反映 HC 注入对器件性能的影响。

6.1.3 由于单级反相器的传输延迟不易获得，可采用由反相器级联构成的环形振荡器的振荡频率作为监测参数。CMOS 反相器环振的振荡频率与每级反相器延迟的关系如公式（1）所示。

式中：

$f$ ——反相器环振的振荡频率与每级反相器延迟；

N——CMOS反相器环形振荡器级数；

$\tau$  ——单级CMOS反相器传输延迟。

6.1.4 通过等效与计算将 HC 注入对器件的影响转化为 HC 注入对环振频率的影响，而环振振荡频率的退化是线性且易测量的物理量。因此，HCl 监测电路将采用环形振荡器作为电路设计的核心，以环振频率的衰退来衡量电路与器件的退化。

## 6.2 HCl 监测方法

6.2.1 要完成芯片内建监测单元，就需对失效程度进行判断。为了判断环形振荡器振荡频率的衰退程度，通过对反相器进行抗衰退加固的方式来保证非退化环形振荡器的振荡频率基本不变。通过比较不断退化的环形振荡器（未进行抗衰退加固）与非退化环形振荡器的频率差异就可达到衰退监测的目的。

6.2.2 监测串路中被监测的环形振荡器由普通的反相器级联组成,且反相器中的 NMOS 的沟道长度可采

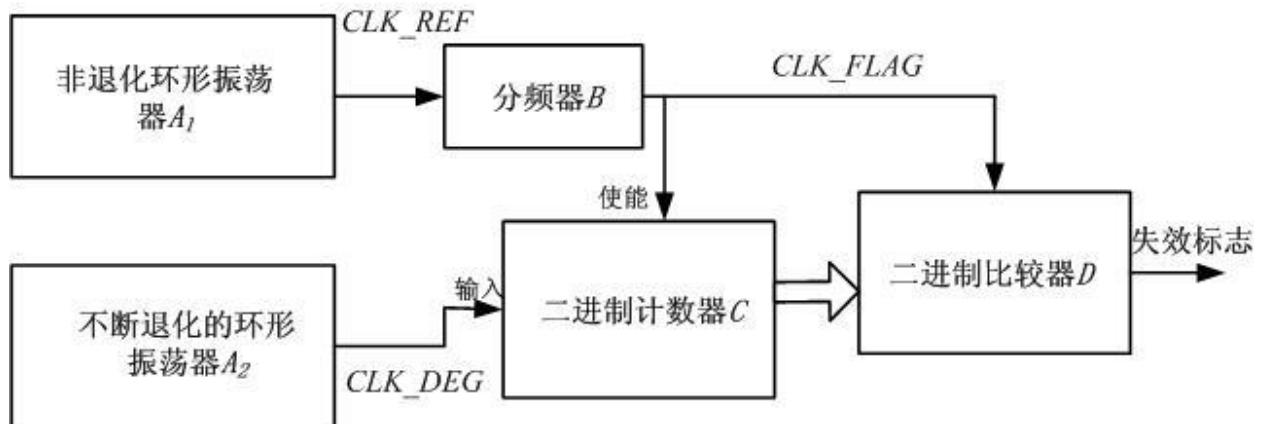

用工艺最小尺寸，监测电路框图如图 1 所示。

图1 监测电路框图

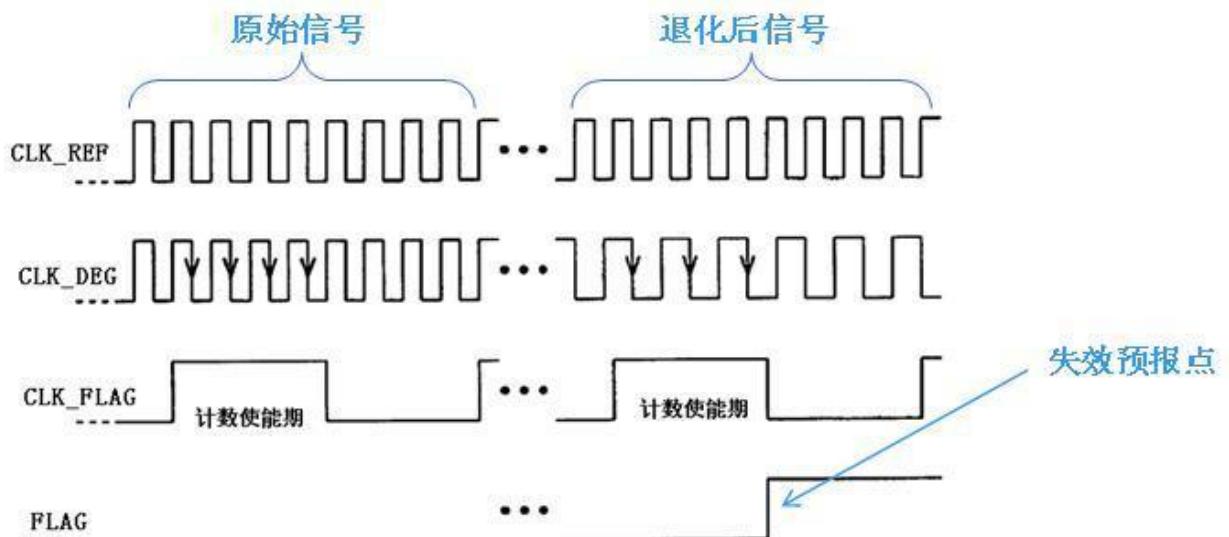

6.2.3 在第一个计数周期到来时，如图 2，计数器开始对  $CLK\_DEG$  信号的脉冲进行计数，并在第一个计数周期的下降沿到来记下脉冲数。将初始脉冲数  $N$  保存作为比较器进行比较的基数。随着 HC 应力的作用，计数器  $C$  记得的脉冲不断减小。在计数使能期间，二进制比较器会将初始脉冲数与频率衰退后记得的脉冲计数  $K$  进行比较。如果两个数值之差小于预先设定的衰退界限  $A$ ，当  $N-K < A$  时，说明环振频率衰退不严重，比较器输出为 0；当  $N-K > A$  时，比较器输出为 1，说明环振频率的衰退较为严重。此时电路发出告警信号，提醒用户采取应对措施。

图2 HC 监测电路总体时序示意图

## 7 设计程序

设计可分为以下步骤：

- 确定工艺方案路线；

- 确定设计功能、性能指标、占用面积、输出形式等的总体目标；

- 进行双环振设计以及监测电路设计；

- 进行主电路内 HC 退化监测单元个数、布局以及具体 I/O 接口设计；

- e) 内建 HC 监测单元版图布局与布线设计;

- f) 电路仿真验证: 按电路原理图及版图进行前后仿真, 验证其正确无误。

## 8 电路设计

### 8.1 一般要求

- 8.1.1 按电路的流程安排各功能单元的位置, 使布局便于信号流通, 并使信号尽可能保持一致的方向。

- 8.1.2 以模块的核心元件为中心, 围绕它进行布局减少和缩短各元器件之间的引线和连接长度。

- 8.1.3 缩短元器件之间的连线, 减少它们的分布参数和相互之间的电磁干扰。易受干扰的元件不应靠近, 输入输出应远离。

- 8.1.4 应综合考虑各元件之间的分布参数。宜使元器件平行排列, 易于批量生产。

- 8.1.5 应注意整个电路的重心平衡与稳定。

### 8.2 非退化环形振荡器设计

- 8.2.1 设计时, 应秉持将监测电路所占用芯片面积减至最小的原则。

- 8.2.2 监测电路设计中衰退环振采用通用的 CMOS 反相器构成的环形振荡器。

- 8.2.3 非退化环形振荡器应采用抗衰反相器构成的环形振荡器。

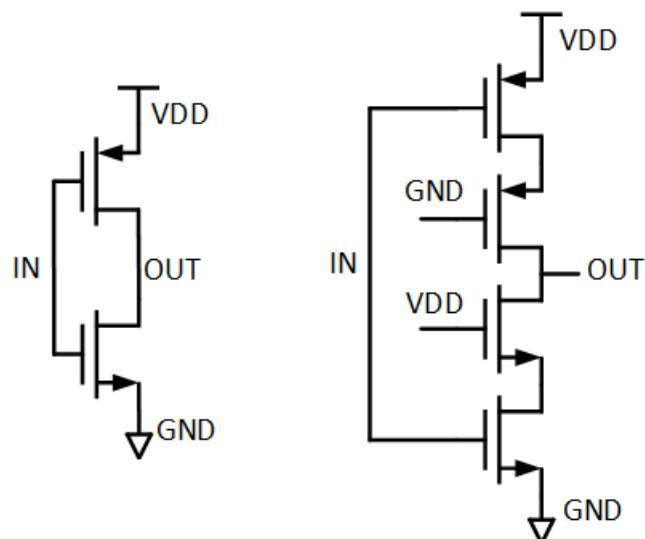

- 8.2.4 由于非退化环形振荡器需为计数器提供计数脉冲, 其振荡频率不宜过高。否则, 在单个计数周期内, 计数器所记录的脉冲数 N 将过小, 进而对监测电路的精度产生负面影响。设计非退化环振时, 分压 MOS 应采用较长沟道的 NMOS, 如图 3 所示。

注: 设计能够更有效地抑制HCI对非退化环振的影响, 使非退化环振的振荡频率更为稳定, 降低频率衰退风险。此外, 长沟道MOS可减小反相器漏电流, 显著降低环振频率。环振频率的降低进而减少分频器所需的级数, 最终实现芯片面积的有效节省。

a) 衰退环振中的反相器单元      b) 非退化环振中的反相器单元

图3 两种环形振荡器中采用的反相器单元结构

### 8.3 HC 注入监测单元电路设计

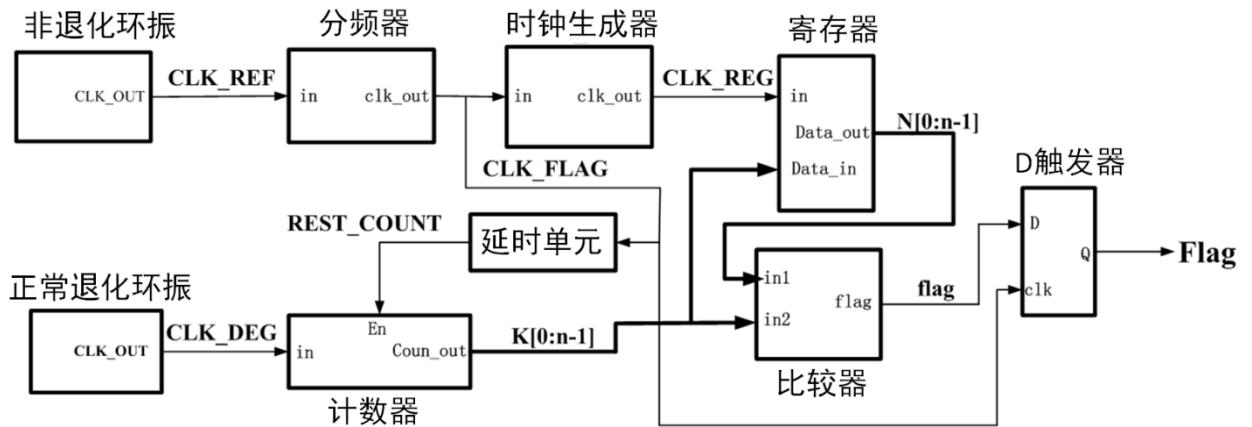

- 8.3.1 HC 失效监测电路的总体框图按图 4 所示。

图4 监测电路设计详细框图

8.3.2 衰退环形振荡器中门电路中MOS管的最小尺寸应采用与被监测电路中的相同。

8.3.3 应采用带清零端的主从D触发器构成D触发器。

8.3.4 二进制计数器应采用带有清零端的主从D触发器。

#### 8.4 布局设计

8.4.1 各器件的排列应尽量紧凑，且保持与主电路的应力耦合。

8.4.2 电路和敏感电路之间的布应尽量隔离，减少电路对敏感电路的干扰。

8.4.3 应保持最短走线，减少两连接节点之间的走线长度和相邻信号线平行走线长度。

8.4.4 相邻层导线应相互垂直或交叉走线，如果有平行走线应尽量减少导线的平行长度。

### 9 测试验证

#### 9.1 测试设备

半导体参数测试仪要求如下：

——源表：能提供满足主芯片电压要求的电压范围，如0 V~10 V；能检测电路静态功耗与漏电的电流范围，如10 pA~1 A；

——示波器：能提供满足主芯片要求的采样范围，如200 MSa/s、10 GSa/s；

——恒温箱：-40 °C~+85 °C；-55 °C~+125 °C。

#### 9.2 试验环境

典型条件：温度：-40 °C~+85 °C；湿度：50%RH~90%RH。

#### 9.3 测试方案

9.3.1 HCI失效实验按以下顺序进行：

- 对未经过抗HC加固的环形振荡器进行加速寿命试验，得出环形振荡器频率随时间的变化曲线，

HCI测试方案如下：

- 监测环形振荡器电路工作是否正常；

- 然后对环形振荡器施加加速退化应力，得出环形振荡器频率随时间的变化曲线。

- 通过加速寿命试验验证HCI失效监测电路的功能，监测电路实验方案如下：

- 用源表及示波器测试电路是否正常；

2) 选取至少 2 个样品进行加速寿命试验，测试监测电路功能。

9.3.2 若两个以上监测电路样品的输出均由低电平变为高电平，则判定芯片内建沟道退化监测单元电路设计正确、设计功能实现。

#### 9.4 测试结果

展示测试结果时，至少应报告以下内容：

- 测试样品数量及其尺寸；

- 使用的应力电压；

- 最先达到的失效准则；

- 测试数据值及其标准差；

- 测试曲线图。

## 参 考 文 献

- [1] IEC 62416-2010 半导体器件 MOS晶体管的热载子试验 (Semiconductor devices – Hot carrier test on MOS transistors)

- [2] CEI EN 62416-2011 半导体器件 金属氧化物半导体晶体管的热载流子测试(Semiconductor devices – Hot carrier test on MOS transistors)

- [3] PNS IEC 62416-2013 半导体器件-MOS晶体管上的热载流子试验 (Semiconductor devices – Hot carrier test on MOS transistors)

-